Sigrity är det mest beprövade verktyget för modellering, signal- och effektintegritetsanalys för PCB och IC.

Sigrity ger highspeed designern allt han behöver. Det är den mest kraftfulla, avancerade sammankopplingsmodelleringen, signal- och effektintegritetssimuleringen för PCB och IC.

Med Cadence® Sigrity™ PowerDC™, med den extra noggrannheten av elektrisk/termisk samsimulering, får du försäkran om att din PDN fungerar som förväntat. Med PowerDC kan du enkelt lokalisera oavsiktliga spänningsförluster, höga strömtätheter, via med för höga strömmar och termiska hotspots. Alla dessa effekter kan avsevärt påverka kvaliteten på designen och begränsa produktens livslängd.

Med Cadence® Sigrity™ OptimizePI™ får du insikt i hur PDN-frekvensegenskaperna ser ut för varje enskild komponent, inklusive plandesign och placering i stackupen, frånkoppling, deras routing och placering, såväl som routing från leveransplaner till komponenter. Placerade kopplingar kan också optimeras vad gäller pris vs. prestanda och verifiera EMI-prestanda genom att mäta impedans för självvalda platser på layouten.

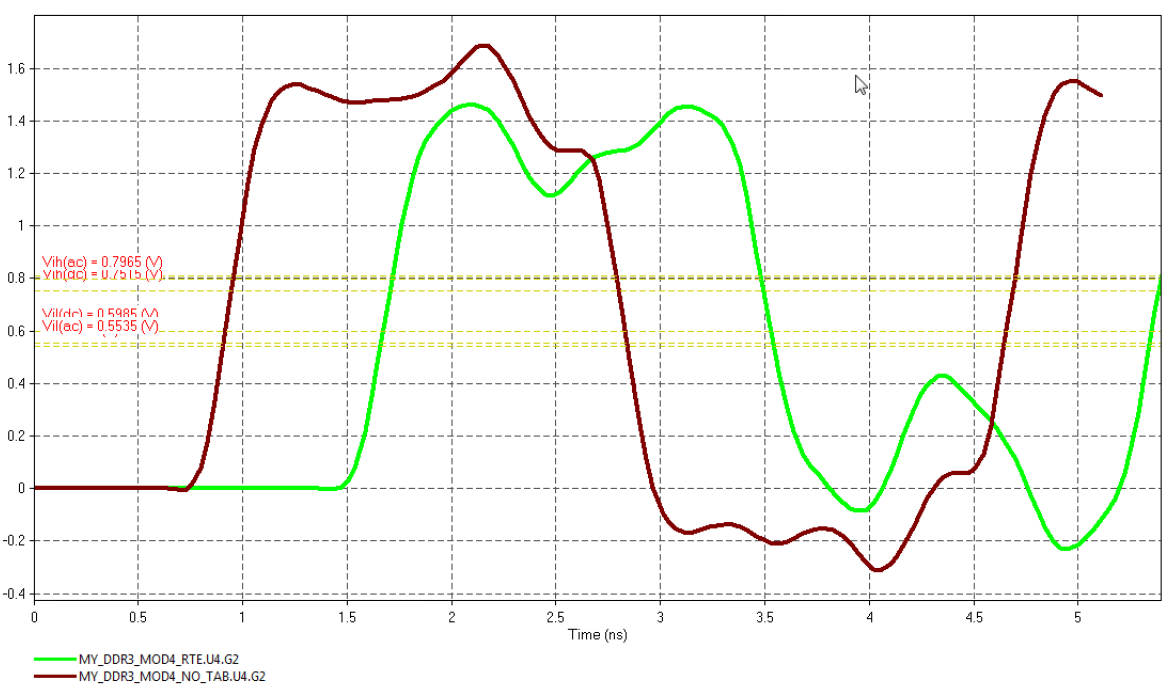

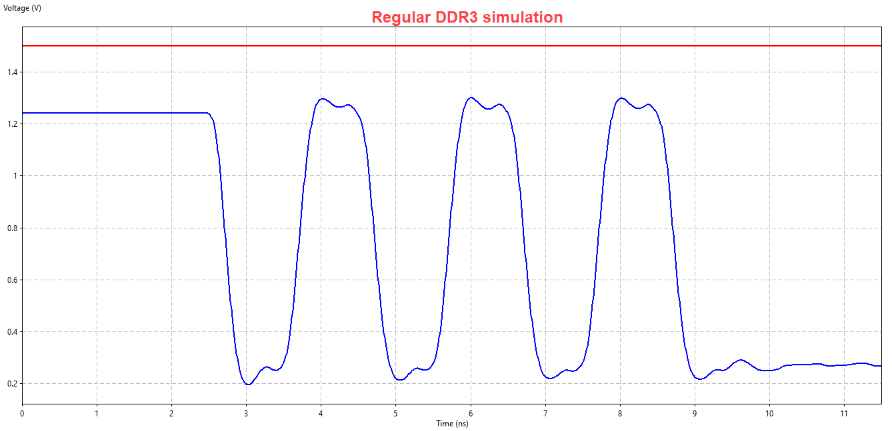

Simultaneous switching noise (SSN) kan ändra timingen på ett minnesgränssnitt. Med Sigrity™ Power-Aware SI får du en komplett lösning för att analysera källsynkrona gränssnitt som används för t.ex. DDR3 och DDR4 minnesgränssnitt. Power-Aware SI innehåller både verktyg för layoutextraktion av banor och förnödenheter samt intuitiva simuleringsverktyg för parallell bussanalys som kan generera rapporter med information om tidsmarginaler som uppfylls enligt JEDEC-standarden.

Med den exponentiella ökningen av konsument-/IoT-enheter överförs zettabytes av data varje år, och systemdesigner förväntas vanligtvis fördubbla överföringshastigheterna vartannat år. Design och analys av multi-gigabit seriella länkar måste vara tillgänglig på ingenjörens skrivbord.

Vi erbjuder teknologi som hjälper dig att analysera och optimera alla avsnitt av den seriella länken. Transceivers och alla förbindelser som kopplar samman chips, paket, kretskort och kontakter kan modelleras och simuleras för att bekräfta att de seriella länkarna i din produkt kommer att uppfylla specifikationerna.

Denna avancerade tillvägagångssätt för analys är viktig för att förstå och förbättra SI/PI i höghastighetsanslutningar, som ofta återfinns i avancerade elektroniska system, såsom molnservrar, telekommunikationsutrustning och konsumentelektronik.